石英振蕩器系列一:幾種輸出波形闡述及應(yīng)用選擇

來源:http://review-result.com 作者:億金電子 2020年10月09

石英振蕩器系列一:幾種輸出波形闡述及應(yīng)用選擇

截止今日,長達8天的小長假已經(jīng)宣告結(jié)束啦,各位都開始全身心的投入到工作中去了,但是我想應(yīng)該還有像小編我一樣依舊對假期戀戀不忘的朋友,但是沒辦法,還是得認真工作呀!尋思著節(jié)后給諸位準(zhǔn)備點干貨,所以接下來的一段時間都會圍繞石英晶體振蕩器為主題;今天我們要討論的是振蕩器的幾種輸出波形以及在應(yīng)用過程中的適應(yīng)性匹配.

只要是學(xué)過模擬電路以及數(shù)字電路并且對石英振蕩器有一定了解的都知道,振蕩器有兩種輸出,一種是單端輸出,一種是雙端輸出,同時它的輸出型號波形也分為好幾種,并且每一種都有差距,這也就導(dǎo)致了我們在應(yīng)用過程中的選擇也會有所不同. 晶振常用的輸出模式主要包括:TTL,CMOS,ECL,PECL,LVDS,Sine Wave.這幾種波形都是目前行業(yè)常用的波形.其中TTL,CMOS,ECL,PECL,LVDS均屬于方波,Sine Wave屬于正弦波.通常,方波輸出功率大,驅(qū)動能力強,但諧波分量豐富;正弦波輸出功率不如方波,但其諧波分量(這是造成相位噪聲的根本原因)小很多.下面就幾種常用的波形進行介紹.

CMOS (互補金屬氧化物半導(dǎo)體CMOS邏輯電路),傳輸延遲時間慢,功耗低,屬于電壓控制器件.CMOS相對TTL有了更大的噪聲容限,輸入阻抗遠大于TTL輸入阻抗.對應(yīng)3.3V LVTTL,出現(xiàn)了LVCMOS,可以與3.3V的LVTTL直接相互驅(qū)動.HCMOS采用全靜態(tài)設(shè)計,高速互補金屬氧化物半導(dǎo)體工藝,CMOS采用互補金屬氧化物半導(dǎo)體.CMOS最終將會被HCMOS所替代,但這都是后話了.

PECL:ECL電路速度快,驅(qū)動能力強,噪聲小,很容易達到幾百MHz的應(yīng)用,但是功耗大,需要負電源.為簡化電源,出現(xiàn)了PECL(ECL結(jié)構(gòu),改用正電壓供電)和LVPECL的輸出模式.LVPECL即是Low Voltage PosiTIve Emitter-Couple Logic(低壓正發(fā)射極耦合邏輯),LVPECL是由ECL和PECL發(fā)展而來,LVPECL的典型輸出為一對差分信號,他們的射極通過一個交流源接地.

LVDS: (低電壓差分信號),為差分對輸入輸出,內(nèi)部有一個恒流源3.5~4mA,在差分線上改變方向和電平來表示“1”和“0”.通過外部的100歐匹配電阻(并接在差分線上靠近接收端)轉(zhuǎn)換為±350mV的差分電平.LVDS使用注意:可以達到600MHz以上,PCB要求較高,差分線要求嚴格等長,差最好不超過10mil(0.25mm);100歐電阻離接收端距離不能超過500mil,最好控制在300mil以內(nèi).

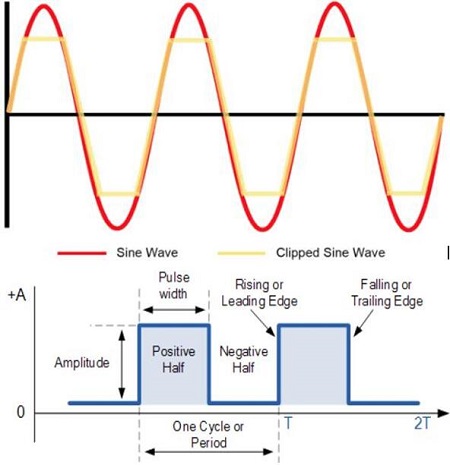

Clipped Sine Wave:削頂正弦波(Clipped Sine Wave).相比方波的諧波分量少很多,但驅(qū)動能力較弱,在負載10K//10PF時Vp-p為0.8Vmin.通常為SMD 7050,SMD5032,SMD3225等封裝的表貼溫補晶振使用的輸出波形.

Sin Wave:通常晶振正弦波輸出的負載阻抗為50歐姆.波形的諧波分量很小,一般諧波抑制都優(yōu)于-30dBc.正弦波輸出晶振通常用于射頻信號處理,頻率源等應(yīng)用場合.

很顯然,這些輸出波形各有千秋,有的功耗過大,相位噪聲過高,但是驅(qū)動功率強大,而有的呢卻是恰恰相反,所以在應(yīng)用和設(shè)計時應(yīng)當(dāng)按需進行選取.

那么我們又依照怎樣的準(zhǔn)則進行呢?自然是以需求為驅(qū)動了;比如你想要的效果是簡便易用的話,那么選用LVDS;如果想要獲得更高頻率的話,LVDS,CMOS,PECL不失為很好的選擇;而當(dāng)輸出頻率大于150MHZ并且要降低功率的話,那CMOS和LVDS就比較合適;除此之外LVDS,LVPECL,CMOS的抖動性能也比較好,所以這三種輸出方式在通常情況下是非常常見的.

那么我們又依照怎樣的準(zhǔn)則進行呢?自然是以需求為驅(qū)動了;比如你想要的效果是簡便易用的話,那么選用LVDS;如果想要獲得更高頻率的話,LVDS,CMOS,PECL不失為很好的選擇;而當(dāng)輸出頻率大于150MHZ并且要降低功率的話,那CMOS和LVDS就比較合適;除此之外LVDS,LVPECL,CMOS的抖動性能也比較好,所以這三種輸出方式在通常情況下是非常常見的.

以上就是有關(guān)本次有源晶振輸出波形討論的全部內(nèi)容了,你學(xué)到了多少呢?如果還是有疑問的話可以致電億金電子資訊相關(guān)詳情.

石英振蕩器系列一:幾種輸出波形闡述及應(yīng)用選擇

截止今日,長達8天的小長假已經(jīng)宣告結(jié)束啦,各位都開始全身心的投入到工作中去了,但是我想應(yīng)該還有像小編我一樣依舊對假期戀戀不忘的朋友,但是沒辦法,還是得認真工作呀!尋思著節(jié)后給諸位準(zhǔn)備點干貨,所以接下來的一段時間都會圍繞石英晶體振蕩器為主題;今天我們要討論的是振蕩器的幾種輸出波形以及在應(yīng)用過程中的適應(yīng)性匹配.

只要是學(xué)過模擬電路以及數(shù)字電路并且對石英振蕩器有一定了解的都知道,振蕩器有兩種輸出,一種是單端輸出,一種是雙端輸出,同時它的輸出型號波形也分為好幾種,并且每一種都有差距,這也就導(dǎo)致了我們在應(yīng)用過程中的選擇也會有所不同. 晶振常用的輸出模式主要包括:TTL,CMOS,ECL,PECL,LVDS,Sine Wave.這幾種波形都是目前行業(yè)常用的波形.其中TTL,CMOS,ECL,PECL,LVDS均屬于方波,Sine Wave屬于正弦波.通常,方波輸出功率大,驅(qū)動能力強,但諧波分量豐富;正弦波輸出功率不如方波,但其諧波分量(這是造成相位噪聲的根本原因)小很多.下面就幾種常用的波形進行介紹.

CMOS (互補金屬氧化物半導(dǎo)體CMOS邏輯電路),傳輸延遲時間慢,功耗低,屬于電壓控制器件.CMOS相對TTL有了更大的噪聲容限,輸入阻抗遠大于TTL輸入阻抗.對應(yīng)3.3V LVTTL,出現(xiàn)了LVCMOS,可以與3.3V的LVTTL直接相互驅(qū)動.HCMOS采用全靜態(tài)設(shè)計,高速互補金屬氧化物半導(dǎo)體工藝,CMOS采用互補金屬氧化物半導(dǎo)體.CMOS最終將會被HCMOS所替代,但這都是后話了.

PECL:ECL電路速度快,驅(qū)動能力強,噪聲小,很容易達到幾百MHz的應(yīng)用,但是功耗大,需要負電源.為簡化電源,出現(xiàn)了PECL(ECL結(jié)構(gòu),改用正電壓供電)和LVPECL的輸出模式.LVPECL即是Low Voltage PosiTIve Emitter-Couple Logic(低壓正發(fā)射極耦合邏輯),LVPECL是由ECL和PECL發(fā)展而來,LVPECL的典型輸出為一對差分信號,他們的射極通過一個交流源接地.

LVDS: (低電壓差分信號),為差分對輸入輸出,內(nèi)部有一個恒流源3.5~4mA,在差分線上改變方向和電平來表示“1”和“0”.通過外部的100歐匹配電阻(并接在差分線上靠近接收端)轉(zhuǎn)換為±350mV的差分電平.LVDS使用注意:可以達到600MHz以上,PCB要求較高,差分線要求嚴格等長,差最好不超過10mil(0.25mm);100歐電阻離接收端距離不能超過500mil,最好控制在300mil以內(nèi).

Clipped Sine Wave:削頂正弦波(Clipped Sine Wave).相比方波的諧波分量少很多,但驅(qū)動能力較弱,在負載10K//10PF時Vp-p為0.8Vmin.通常為SMD 7050,SMD5032,SMD3225等封裝的表貼溫補晶振使用的輸出波形.

Sin Wave:通常晶振正弦波輸出的負載阻抗為50歐姆.波形的諧波分量很小,一般諧波抑制都優(yōu)于-30dBc.正弦波輸出晶振通常用于射頻信號處理,頻率源等應(yīng)用場合.

很顯然,這些輸出波形各有千秋,有的功耗過大,相位噪聲過高,但是驅(qū)動功率強大,而有的呢卻是恰恰相反,所以在應(yīng)用和設(shè)計時應(yīng)當(dāng)按需進行選取.

以上就是有關(guān)本次有源晶振輸出波形討論的全部內(nèi)容了,你學(xué)到了多少呢?如果還是有疑問的話可以致電億金電子資訊相關(guān)詳情.

石英振蕩器系列一:幾種輸出波形闡述及應(yīng)用選擇

正在載入評論數(shù)據(jù)...

相關(guān)資訊

- [2024-05-24]Silicon超小型EFR32BG27推動無線口腔...

- [2024-05-22]Rakon推出了首款集成電路ROM1490X支持...

- [2024-04-23]Raltron濾波器RSF-110.592-280-7050-...

- [2024-04-19]Abracon低功率HCSL清晰時鐘振蕩器AK2...

- [2024-04-17]PETERMANN高精度SXO18-02502-S-E-25-...

- [2024-04-15]ECS醫(yī)療設(shè)備設(shè)計應(yīng)用晶振ECS-2033-24...

- [2024-04-13]Statek晶振CXOXLPN4DSNSM3-25.0M.50/...

- [2024-04-11]MtronPTI組件和子組件設(shè)計和測試能力...

銷售代表

銷售代表